| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 | 31 |

- GPIO

- terminal

- 7 세그먼트

- MAC OS

- bldc

- CCS

- St

- easyeda

- 마이컴

- 모두의연구소

- mcu

- JLCPCB

- m4

- RTOS

- 8051

- 임베디드

- TM4C123GXL

- PCB

- Embedded System

- Developer

- 아트웍

- 임베디드시스템

- EMBEDDED

- TI

- Arm

- IoT

- Programming

- TM4C123

- 전자공학

- 초보개발자

- Today

- Total

Engineering Agit

[Session 02 TM4C123GXL Study 02] - GPIO 03 본문

[Session 02 TM4C123GXL Study 02] - GPIO 03

Sean_Kim95 2020. 8. 22. 17:17◈ 본 글은 지난 '[Session 02 TM4C123GXL Study 02] - GPIO 02'에 이어진다.

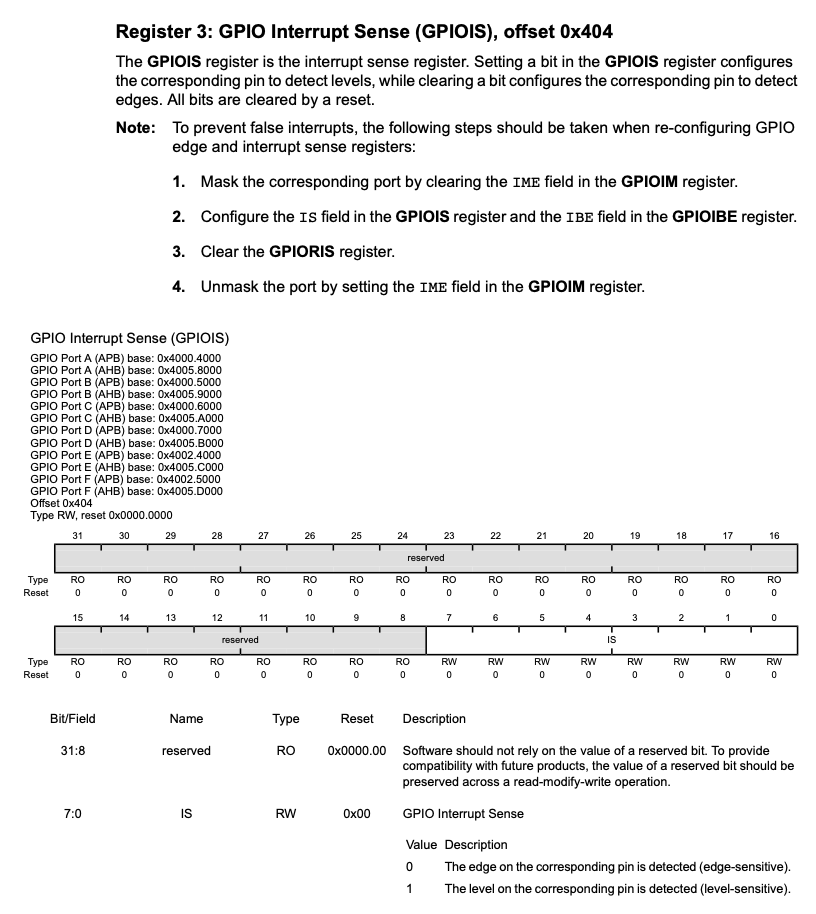

2. Interrupt control

각각의 GPIO 핀의 interrupt는 7개의 register들에 의해 제어된다. 이들 register들은 interrupt source, interrupt 우선순위, 그리고 edge property들(interrupt 인식을 rising-edge에서 할 것인지, falling-edge에서 할 것인지 아니면 이 두개가 결합된 형태로 할 것인지)을 선택하는 용도로 사용된다. 한개 또는 다수의 GPIO input이 interrupt를 발생시키면, 한개의 interrupt output이 전체 GPIO port의 control을 위한 interrupt controller에 보내진다. Edge-triggered interrupt들을 control하기 위해서는, SW적으로 해당 interrupt를 이후의 interrupt들을 위해 clear한다. Level-sensitive interrupt를 위해서는 해당 interrupt를 controller가 인지하게 하기 위해서 외부의 source를 일정한 값으로 주어야한다.

아래의 세 register들은 interrupt를 발생시키는 edge 혹은 sense를 정의한다.

-

GPIOIS(Interrupt Sense) register:

-

GPIOIBE(Interrupt Both Edges) register:

-

GPIOIEV(Interrupt Event) register:

이외에 4개의 register가 있는데 세부 내용은 다음과 같다.

-

GPIOIM(Interrupt Mask) register: Interrupt enable/disable을 설정하는 register.

Interrupt condition이 발생했을 때, interrupt signal의 상태는 GPIORIS와 GPIOMIS 두 곳에서 확인이 가능하다. 이름이 암시하는 바와 같이 GPIOMIS의 경우에는 interrupt controller를 통과한 interrupt condition만을 보여준다. GPIORIS의 경우에는 interrupt condition의 input signal이 GPIO 핀에 들어온 것을 보여주지만, interrupt controller에 보내진 signal일 필요는 없다.

GPIO level-detect interrupt를 위해서, interrupt를 발생시키는 interrupt signal은 반드시 처리되기 전에 hold될 필요가 있다. Interrupt generating logical sense에서 input signal이 한 번 deassert(active에서 inactive로 바뀌는 것)되면, 이에 상응하는 GPIORIS reg.의 RIS bit가 clear된다. GPIO edge-detect interrupt를 위해, 상응하는 GPIOICR reg.의 bit를 set하여 GPIORIS reg.의 해당 bit를 clear한다. 상응하는 GPIOMIS bit는 RIS bit의 값을 반영한다.

-

GPIORIS(Raw Interrupt Status) register:

-

GPIOMIS(Masked Interrupt status) register:

-

GPIOICR(Interrupt Clear) register:

Interrupt control register들(GPIOIS, GPIOIBE, 혹은 GPIOIEV)을 프로그래밍할 때, interrupt들은 mask(GPIOIM을 clear함으로써)되어있어야 한다. Mask되어있지 않은 상태에서 위의 세 register에 값을 쓰게되면 불필요한 interrupt가 발생할 수 있다.

2-1. ADC trigger source

모든 GPIO 핀은 GPIOADCCTL(GPIO ADC Control) reg.를 이용하여 ADC를 위한 외부 trigger로 설정할 수 있다. 만약 어떤 GPIO의 해당 GPIOIM의 bit가 set되어 non-masked interrupt 핀으로 설정되어 있다면, 해당 포트에 interrupt가 발생되고, trigger signal이 ADC에 보내진다. 만약 ADCEMUX(ADC Event Multiplexer Select)가 외부 trigger로 사용하기 위해 설정된다면, ADC conversion이 시작된다.

※ 포트 B의 경우에는 GPIOADCCTL reg.가 clear되더라도 PB4는 여전히 ADC의 외부 trigger로 사용될 수 있다. 이는 해당 MCU에서 이전의 device들을 사용하기 위해 쓰여진 code를 허용할 수 있게 하는 legacy mode이다. (https://en.wikipedia.org/wiki/Legacy_mode#:~:text=In%20computing%2C%20legacy%20mode%20is,%2C%20data%2C%20or%20expected%20behavior.)

Legacy mode - Wikipedia

In computing, legacy mode is a state in which a computer system, component, or software application behaves in a way that is different from its standard operation in order to support older software, data, or expected behavior. It differs from backward comp

en.wikipedia.org

2-2. uDMA trigger source

모든 GPIO 핀은 GPIODMACTL(GPIO DMA Control) reg.를 이용하여 uDMA의 외부 trigger로 설정이 가능하다. 만약 어떤 GPIO의 해당 GPIOIM의 bit가 set되어 non-masked interrupt 핀으로 설정되어 있다면, 해당 포트에 interrupt가 발생되고, trigger signal이 uDMA에 보내진다. 만약 uDMA가 GPIO signal에 기반하여 transfer을 시작하도록 설정되어있다면, 그 transfer가 시작된다.

Tiva™ C Series TM4C123GH6PM Microcontroller Data Sheet (Rev. E)

'Embedded Lab. @ Modu inst. > 2020 Session 02 (2020.06~)' 카테고리의 다른 글

| [Session 02 TM4C123GXL Study 02] - GPIO 04 (0) | 2020.10.04 |

|---|---|

| [Session 02 TM4C123GXL Study 01] - How to create new project in CCS (0) | 2020.09.25 |

| [Session 02 TM4C123GXL Study 03] - Programming methods with CCS (0) | 2020.08.11 |

| [Session 02 TM4C123GXL Study 02] - GPIO 02 (0) | 2020.08.07 |

| [Session 02 TM4C123GXL Study 02] - GPIO 01 (0) | 2020.07.28 |